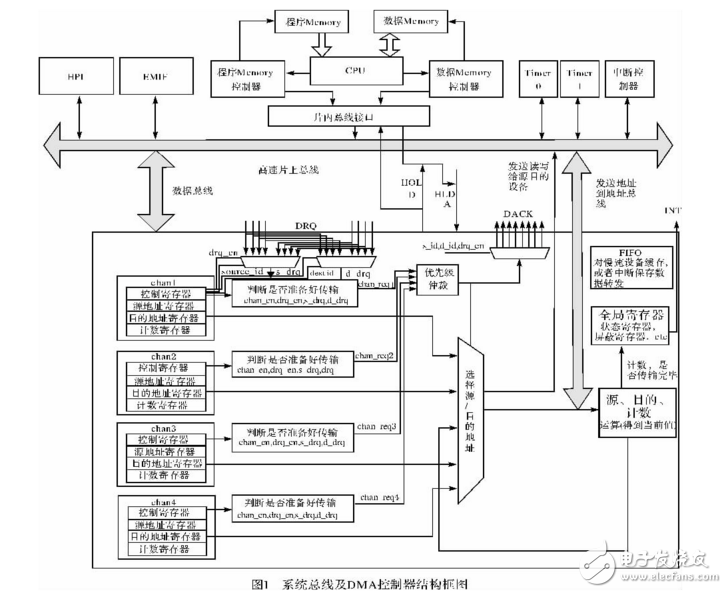

In the computer system, in order to speed up the transmission of large quantities of data, the DMA method is often used, which is realized by integrating the on-chip DMA controller interface components, and directly opens the data channel between the memory and the peripherals, and the access strategy and control of the DMA controller. The quality of the agreement directly affects the performance of the entire processor system14. The system uses SystemC system-level design language to implement a fast configurable multi-function DMA controller. The SystrmC language was introduced in 1999 and is supported by OSCI. Maintenance and development goals. It is an open system-level design language based on C++. It can support both software-level and hardware-level modeling. It can implement software and hardware co-simulation, and can gradually refine the system to the register transfer level for comprehensive. Effectively simplify the design process, reduce design time and cost. The peripheral device communicates with the core or sends control information through different types of buses. O. In order to improve the efficiency of the whole system, there are often different levels of buses in the processor, which are used to connect different devices. The first-level internal bus is often used to achieve direct access to the internal memory by the core; the secondary system peripheral bus is used to achieve high-speed access between the peripheral and the internal memory; the tertiary bus is used to connect to lower-speed peripherals. And connected to the secondary bus through a bridge. The DMA controller is also equivalent to a peripheral, followed by an interrupt controller timer. External memory interface, host interface. The on-chip memory interface is connected together on the secondary peripheral bus. The DMA controller is mainly composed of the following parts: Register status register, control register, and address register. Count register and mask register). The data buffer is used to receive data sent from the source device and wait for forwarding to the destination device). Address counter arithmetic unit, priority arbitration logic. Interrupt control logic. The specific structure of the peripheral bus DMA controller is shown in Figure 1. (The figure shows a four-channel DMA controller only, and the DMA controller architecture of more channels is similar). China manufacture for Popular Custom Vape Pen, high quality battery, quality e-liquid and food safty material. Prefilled Vape Newmax Electronics Co.,Limited , https://www.advvape.com

1 Introduction