Abstract: This article introduces the principle of a zero-IF receiver, and the design and implementation of a zero-IF receiver based on the high-performance modem chip HFA3787. Introduction As we all know, the traditional "superheterodyne" wireless receiver work process is as follows: weak high-frequency radio signals must pass through one or several stages of mixing circuits to remove interference from other channels and obtain sufficient gain, and finally complete Demodulate and extract the required information. HFA3783 chip function and structure Parameter setting and register function Circuit realization of similar zero-IF receiver Because the radio frequency section adopts the traditional structure, we will not repeat it here. Its circuit block diagram is shown as in Fig. 4. Conclusion Because in addition to the modulation and demodulation circuits, HFA3783 also integrates IF amplifier, AGC, baseband low-pass filtering and other circuits. In this way, the IF circuit of the zero-IF receiver requires only a few components, and it is also easy to debug. It is more convenient; and HFA3783 can also provide a 1.2V reference level for A/D sampling to improve the accuracy of A/D sampling. Piezoelectric Buzzer For External Drive The piezoelectric transducers (for External

Drive) produce exceptional sound output and efficiency all while meeting each

customers unique performance requirements. Piezo transducers are constructed

without magnets, instead they create sound mechanically via the piezoelectric effect.

Our piezo transducers are not equipped with a built in drive circuit. This

provides our customers with the flexibility of designing their own circuitry to

meet their specific needs. The advantage of using an external drive circuit is

that the piezo transducers can output sounds at multiple frequencies. Full

bridge circuits ramp up SPL for more peak-to-peak voltage, making our piezo

transducers a high output solution.

Piezo Alarm Buzzer,Alarm Piezo Buzzer,Fire Alarm Piezo Buzzer,Active Magnetic Buzzer Jiangsu Huawha Electronices Co.,Ltd , https://www.hnbuzzer.com

In order to overcome the defects of "superheterodyne" wireless receivers such as image interference and the need for high-Q filters, the concept of zero-IF receivers has been proposed. This structure, called Direct-Conversion or Zero-IF, has the following advantages: (1) The IF frequency is zero, and there is no image interference problem; (2) The channel selection is performed at low frequencies, which can be It is convenient to use the integrated circuit to digitize the signal.

However, zero-IF receivers also have obstacles that are not easy to eliminate, such as DC offset and low-frequency noise. Therefore, a dual-conversion wih Wideband Fisrt IF receiver has been proposed. This kind of receiver changes the high frequency signal to a higher intermediate frequency during the first frequency conversion, and the output of the second frequency conversion is zero intermediate frequency. This article adopts the structure of this kind of zero-IF receiver. Figure 1 shows its working principle diagram.

HFA3783 is a comprehensive chip introduced by Intersil for half-duplex wireless applications. It contains all the necessary functional modules for quadrature modulation and I/Q channel demodulation. Its intermediate frequency receiving AGC amplifier has a 600 MHz frequency response range and 70 dB voltage gain, and has a gain control range of more than 70 dB; the transmit output also has a gain control range of 70 dB. Its receiving and transmitting intermediate frequencies can share a differential matched filter network to reduce the number of filter components necessary in a single intermediate frequency half-duplex transmitter. In the receiving mode, there are functions such as DC offset correction circuit and intermediate frequency level detection. The internal mixer is driven by a wideband quadrature local oscillator generator, and the intermediate frequency setting and PLL loop synchronization parameters are controlled by a 3-wire serial interface. It only requires a low-level external VCO and a reference with a frequency of up to 50 MHz. source. Its function module is shown as in Fig. 2.

Its main features are as follows:

It integrates all the functions of IF transmission and reception. The wide range of orthogonal frequency ranges from 70 to 600MHz, and the IF AGC dynamic range is 69dB. It has a DC coupling baseband interface and a receiving DC offset correction loop. It is controlled by a 3-wire serial interface. PLL loop synchronization, local oscillator drive level is -15dBm, transmit/receive function switch <1μs, with power management/wait mode and single voltage (2.7V~3.3V) power supply.

Figure 1 Schematic diagram of double-conversion wide-IF receiver

Figure 2 HFA3783 functional module diagram

Figure 3 Timing diagram of synchronous serial port

Figure 4 Block diagram of the circuit of a zero-IF receiver

Because HFA3783 is a half-duplex mode, it needs to input pins PE1, PE2 and the lowest bit M(0) of register M to define the working status of sending/receiving. Its truth table is shown in Table 1.

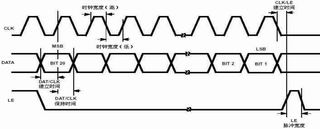

HFA3783 has 5 internal function registers, all of which are set through a 3-wire serial interface. The 3 input pins are: clock (CLK), data (DATA), and latch (LE). The input timing is shown in the figure 3 shown.

When the data input is full of 20 bits, input a latch signal, HFA3783 judges which register is set by comparing the lower 2 bits of data. The specific settings are shown in Table 2.

Among them, R is the frequency division ratio of the reference source, and A/B and M(2) are the VCO frequency division coefficients. HFA3783 controls the tuning voltage of the VCO by comparing the divided reference frequency REF/R with the divided VCO/[P*B+A], and finally makes the PLL loop lock to the frequency set by the user.

The value of the C register determines the frequency and time for correcting the DC bias level in the receiving mode. The calculation formula for the correction time is:

Correction time=22&TImes;

Among them fREFIN is MHz grade.

M is the working mode register, it must be set first, followed by other registers.

Here, use FPGA to configure the parameters of HFA3783, and use FPGA and DSP to process baseband data together. In baseband processing, the low-level signal preprocessing algorithm processes a large amount of data and requires high processing speed, but the computational structure is relatively simple, so it is suitable for hardware implementation with FPGA. In contrast, the amount of data processed by the high-level processing algorithm is relatively small, but the control structure of the algorithm is complex, and it is suitable for implementation with a DSP chip with high computing speed, flexible addressing mode, and powerful communication mechanism.

However, we found several problems during hardware debugging that must be paid attention to:

* The frequency division coefficient of the VCO and the reference frequency is a contradiction with the phase noise of the PLL loop of the local oscillator: if the frequency division coefficient is selected small, the PLL loop may not be able to lock normally; if the frequency division coefficient is selected large, the phase noise of the PLL loop is also Correspondingly increased, which requires specific debugging to choose a compromise solution.

* Impedance matching requires careful consideration. The intermediate frequency input and output terminals of HFA3783 can share a filter matching network with an impedance of 250W.

* The transmitter baseband of HFA3783 needs a bias voltage of 1.3V, otherwise the transmitter IF will not work normally.

The scheme of the zero-IF receiver introduced in this article has been successfully applied to a certain type of spread spectrum unit, and all performance indicators have reached the requirements.